# HPI Future SOC Lab: Proceedings 2012

Christoph Meinel, Andreas Polze, Gerhard Oswald, Rolf Strotmann, Ulrich Seibold, Bernhard Schulzki (Hrsg.)

**Technische Berichte Nr. 85**

des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.dnb.de/ abrufbar.

#### Universitätsverlag Potsdam 2014

http://verlag.ub.uni-potsdam.de/

Am Neuen Palais 10, 14469 Potsdam Tel.: +49 (0)331 977 2533 / Fax: 2292 E-Mail: verlag@uni-potsdam.de

Die Schriftenreihe **Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam** wird herausgegeben von den Professoren des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam.

ISSN (print) 1613-5652 ISSN (online) 2191-1665

Das Manuskript ist urheberrechtlich geschützt. Druck: docupoint GmbH Magdeburg

#### ISBN 978-3-86956-276-6

Zugleich online veröffentlicht auf dem Publikationsserver der Universität Potsdam: URL http://pub.ub.uni-potsdam.de/volltexte/2014/6899/URN urn:nbn:de:kobv:517-opus-68991 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus-68991

# **Contents**

| Spring 2012                                                                                          |            |

|------------------------------------------------------------------------------------------------------|------------|

| Prof. Dr. Ben Juurlink, Architektur eingebetteter Systeme, Technische Universitä<br>Berlin           | t          |

| Parallelizing H.264 Decoding with OpenMP Superscalar                                                 | 1          |

| Prof. Dr. Jürgen Döllner, Computer Graphics Systems, Hasso-Plattner-Institut                         |            |

| Service-Based 3D Rendering and Interactive 3D Visualization                                          | 7          |

| Dr. Ralf Kühne, SAP Innovation Center, Potsdam                                                       |            |

| Benchmarking and Tenant Placement for Efficient Cloud Operations                                     | 11         |

| Prof. Dr. Christoph Meinel, Internet-Technologies and Systems Group, Hasso-Plattne<br>Institut       | r-         |

| Towards Multi-Core and In-Memory for IDS Alert Correlation: Approaches and Capabilities .            | 15         |

| Multicore-Based High Performance IPv6 Cryptographically Generated Addresses (CGA)                    | 21         |

| Blog- Intelligence Extension with SAP HANA                                                           | 27         |

| Accurate Mutlicore Processor Power Models for Power-Aware Resource Management                        | 29         |

| VMs Core-allocation scheduling Policy for Energy and Performance Management                          | 35         |

| Prof. Dr. Andreas Polze, Operating Systems & Middleware Group, Hasso-Plattner<br>Institut            | · <b>_</b> |

| Parallelization of Elementary Flux Mode Enumeration for Large-scale Metabolic Networks               | 41         |

| Dr. Felix Salfner, SAP Innovation Center, Potsdam                                                    |            |

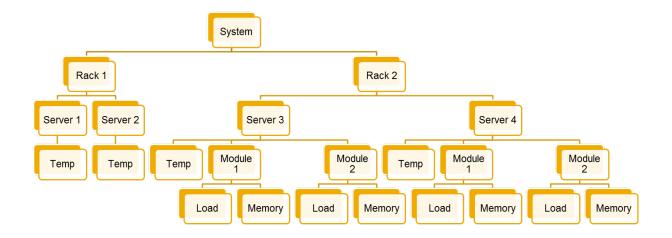

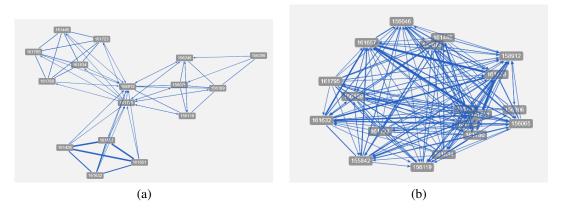

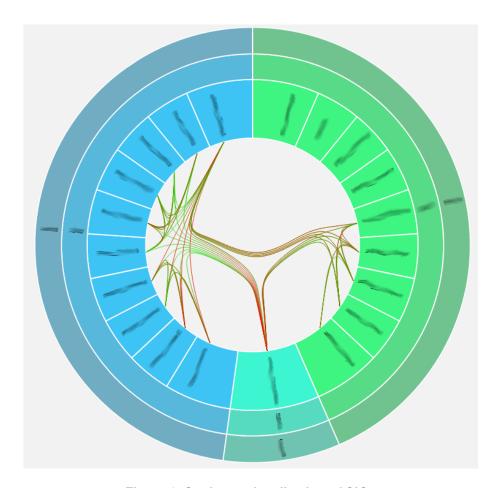

| Early Anomaly Detection in SAP Business ByDesign                                                     | 47         |

| Prof. Dr. Michael Schöttner, Betriebssysteme, Universität Düsseldorf                                 |            |

| ECRAM (Elastic Cooperative Random-Access Memory)                                                     | 53         |

| Prof. Dr. Steffen Staab, Institute for Web Science and Technologies, Universitä<br>Koblenz-Landau    | t          |

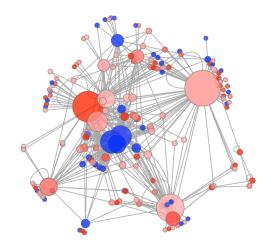

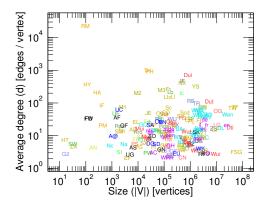

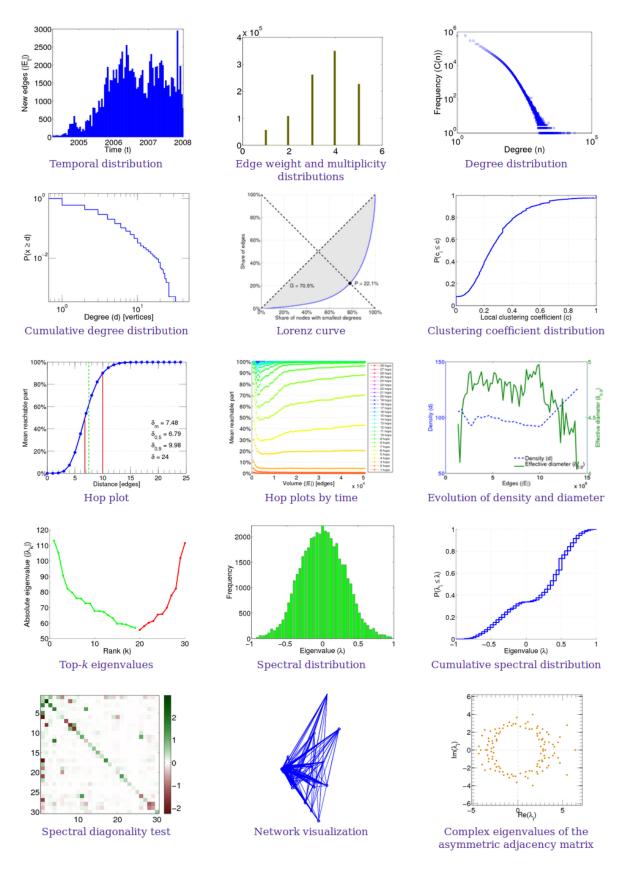

| KONECT Cloud — Large Scale Network Mining in the Cloud                                               | 55         |

| Prof. Dr. Rainer Thome, Chair in Business administration and business computing Universität Würzburg | 5,         |

| Integrated Management Support with Forward Business Recommendations                                  | 59         |

# Fall 2012

| Prof. Dr. Jürgen Döllner, Hasso-Plattner-Institut Potsdam                                          |

|----------------------------------------------------------------------------------------------------|

| Service-Based 3D Rendering and Interactive 3D Visualization                                        |

| Prof. Dr. Jorge Marx Gómez, Carl von Ossietzky University Oldenburg                                |

| Smart Wind Farm Control                                                                            |

| Prof. Dr. Helmut Krcmar, Technical University of Munich                                            |

| Measurement of Execution Times and Resource Requirements for single user requests 6                |

| Dr. Ralph Kühne, SAP Innovation Center Potsdam                                                     |

| Benchmarking for Efficient Cloud Operations                                                        |

| Prof. Dr. Christoph Meinel, Hasso-Plattner-Institut Potsdam                                        |

| Instant Intrusion Detection using Live Attack Graphs and Event Correlation                         |

| Prof. Dr. Andreas Polze, Hasso-Plattner-Institut Potsdam                                           |

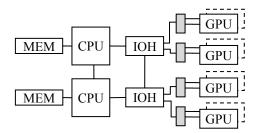

| Exploiting Heterogeneous Architectures for Algorithms with Low Arithmetic Intensity                |

| Dr. Felix Salfner, SAP Innovation Center Potsdam                                                   |

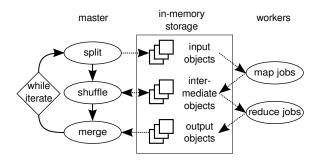

| Using In-Memory Computing for Proactive Cloud Operations                                           |

| Prof. Dr. Kai-Uwe Sattler, Ilmenau University of Technology                                        |

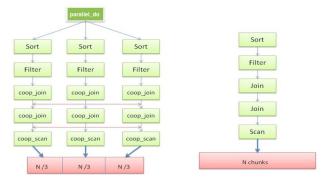

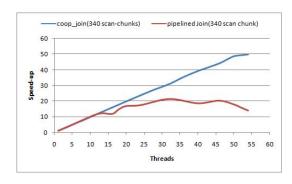

| Evaluation of Multicore Query Execution Techniques for Linked Open Data                            |

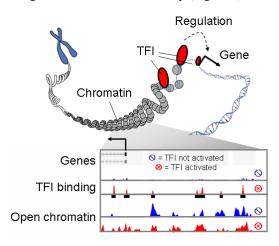

| Dr. Sascha Sauer, Max Planck Institute for Molecular Genetics (MPIMG) Berlin                       |

| Next Generation Sequencing: From Computational Challenges to Biological Insight 9                  |

| Prof. Dr. Michael Schöttner, Heinrich Heine University of Düsseldorf                               |

| ECRAM (Elastic Cooperative Random-Access Memory)                                                   |

| Prof. Assaf Schuster, HPI research school, Technion IIT                                            |

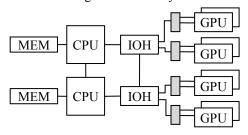

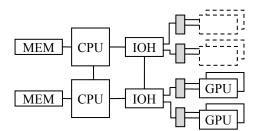

| Analysis of CPU/GPU data transfer bottlenecks in multi-GPU systems for hard real-time data streams |

| Prof. Dr. Steffen Staab, University of Koblenz and Landau                                          |

| KONECT Cloud — Large Scale Network Mining in the Cloud                                             |

| Prof. Dr. Rainer Thome, University of Würzburg                                                     |

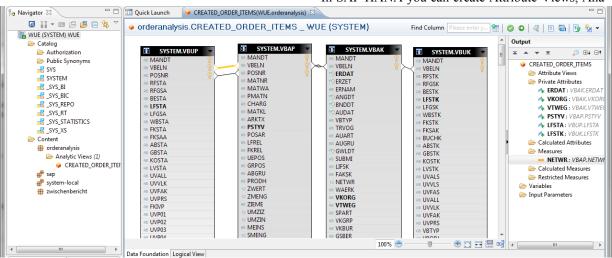

| Adaptive Realtime KPI Analysis of ERP transaction data using In-Memory technology 11               |

| Till Winkler, Humboldt University of Berlin                                                        |

| The Impact of Software as a Service                                                                |

## Parallelizing H.264 Decoding with OpenMP Superscalar

Chi Ching Chi, Ben Juurlink Embedded Systems Architecture Einsteinufer 17 10551 Berlin {chi.c.chi,b.juurlink}@tu-berlin.de

#### **Abstract**

Since the advent of multi-core processors and systems, programmers are faced with the challenge of exploiting thread-level parallelism (TLP). In the past years several parallel programming models have been introduced to simplify the development of parallel applications. OpenMP Superscalar is a novel task-based programming model, which incorporates advanced features such as automated runtime dependency resolution, while maintaining simple pragma-based programming for C/C++. We have parallelized H.264 decoding using OpenMP Superscalar to investigate its ease-of-use and performance.

#### 1 Introduction

Because multi-core processors have become omnipresent, there is a lot of renewed interest in parallel programming models that are easy to use while being expressive, and allow to write performance-portable applications. An important question is, however, how to evaluate the ease of use, expressiveness, and performance of a programming model. In this work we try to answer this question by describing our experiences in parallelizing H.264 decoding using OmpSs, a novel task-based parallel programming model. To evaluate its performance, the performance of the OmpSs application is compared to a similary structured Pthreads applications. H.264 decoding is an excellent case study because it is highly irregular and dynamic, exhibits many different types of data dependencies as well as rather fine-grained tasks, and requires different types of parallelism to be exploited.

In OmpSs [3], in addition to OpenMP functionality, programmers can express parallelism by annotating certain code sections (typically functions) as *tasks*, as well as the *inputs*, *outputs*, and *inputs/outputs* of these tasks. When these functions are called, they are added to a task graph instead of being executed. The task dependencies are resolved at runtime, using the input/output specification of the function arguments.

Once all input dependencies of a task are resolved, it is scheduled for execution.

A key difference between OmpSs and other task-based parallel programming models is the ability to add tasks before they are ready to execute. This is a powerful feature which allows more complex parallelization strategies that simultaneously exploit function-level and data-level parallelism. In this paper we show how these features can be used to implement a parallel implementation of H.264 decoding.

The structure of this paper is as follows: Sections 2 to 5 describe the implementation and optimization of parallel H.264 video decoding using OmpSs. In Section 6 the performance of the OmpSs version is evaluated and compared to an optimized Pthreads implementation. Conclusions are drawn in Section 7.

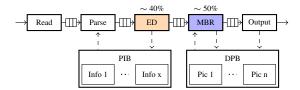

#### 2 Pipelining H.264

The H.264 decoder pipeline consists in our design of 5 pipeline stages, shown in Figure 1. In the read stage the bitstream is read from the disk and parsed into separated frames. In the parse stage the headers of the frame are parsed and a picture info entry in the picture info buffer (PIB) is allocated. The entropy decode (ED) stage performs a lossless decompression by extracting the syntax elements for each macroblock in the frame. Some syntax elements are directly processed, e.g. the motion vectors differences are transformed into motion vectors. The macroblock reconstruction stage allocates a picture in the decoded picture buffer (DPB) and reconstructs the picture using the syntax elements and motion vectors. The output stage reorders and outputs the decoded pictures either to an output file or the display.

In contrast to other task-based programming models, like Cilk++ [7] and OpenMP [2], pipeline parallelism can be straightforwardly expressed in OmpSs, because OmpSs tasks can be spawned before its dependencies have been resolved [8, 6]. Listing 1 presents the simplified code of the pipelined main decoder loop using OmpSs pragmas. A task is created for each pipeline stage in each loop iteration. For correct pipelining of the tasks, it is required that all tasks in iteration *i* are

Figure 1. H.264 decoder pipeline stages in our design

executed in-order. To accomplish this, each task in the same iterations is linked to the previous task in the same iteration via one or more input and output/inout pairs. Additionally, task T of iteration i must be completed before the instance of the same task T in iteration i+1 is started. To accomplish this, each task has a context structure that is annoted as inout, e.g., Read-Context \*rc, NalContext \*nc, EntropyContext \*ec, etc. The pipeline parallelism is uncovered by using entry of a circularly buffer of size N for the task inputs and outputs. This eliminates the WAR and WAW hazards that would have occurred if the same entry is used in each iteration, which would eliminate all the parallelism. Exploiting the FLP, however, is not enough to get scalable performance. The performance of the pipelined implementation is limited by the longest stage in the pipeline. The entropy decode and macroblock reconstruct stages take around 40% and 50% of the total execution time, respectively. The total speedup is in this case limited to a factor of two. To gain additional speedups both the entropy decode and macroblock reconstruct stages must be further parallelized. Both these stages exhibit DLP and how they can be exploited is discussed in the following sections.

#### 3 Parallelizing Entropy Decoding

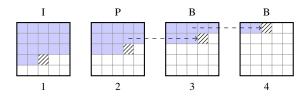

The ED stage performs entropy decoding using CABAC or CAVLC. In both these methods the interpretation of each bit in the stream depends on the previous bit. Therefore, no task parallelism exists inside the entropy decode of one frame. Multiple frames, however, can be decoded in parallel as they are separated by start codes. The frames, however, are not fully independent as illustrated in Figure 2.

In Figure 2, four frames are decoded in parallel. The hatched blocks represent the current MBs that are decoded in parallel and the blue blocks denote the already processed MBs in each frame. For blocks in the B-frames some blocks may need the motion vectors of the co-located block in the previous frame. To express this parallelism, the code segment in Listing 2 can be used replacing the entropy\_decode\_task in Listing 1. The entropy decode task is split in three tasks. The init task initializes the context tables, the decode\_entropy\_line\_task entropy decodes a mac-

```

#pragma omp task inout (*rc) output (*frm)

void read_frame_task(ReadContext *rc, EncFrame *frm

#pragma omp task inout(*nc, *frm) output(*s)

void parse_header_task(NalContext *nc, Slice *s,

EncFrame *frm);

#pragma omp task inout(*ec, *s) input(*frm) output(

*mbs)

void entropy_decode_task(EntropyContext *ec, Slice

*s,

EncFrame *frm, H264mb *mbs);

#pragma omp task inout(*rc) input(*s, *mbs) output(

void reconstruct_task(MBRecContext *rc, Slice *s,

H264Mb *mbs, Picture *pic);

#pragma omp task inout(*oc) input(*pic)

void output task(OutputContext *w, Picture *pic);

EncFrame frm[N]; Slice slice[N];

H264Mb *ed_bufs[N]; Picture pic[N];

int k=0;

while(!EOF){

read frame task(rc, &frm[k%N]);

parse_header_task(nc, &slice[k%N],

&frm[k%N]);

entropy_decode_task(ec, &slice[k%N], &frm[k%N],

ed bufs[k%N]):

reconstruct task (rc. &slice[k%N], ed bufs[k%N],

&pic[k%N]);

output_task(oc, &pic[k%N]);

#pragma omp taskwait on (*rc)

```

Listing 1. Pipelining the main decoder loop using OmpSs pragmas

Figure 2. Parallelism in entropy decoding in multiple consecutive frames. Colored MBs have been entropy decoded. Hatched blocks are decoded in parallel.

roblock line of the picture, and the release task releases one or more Picture Info entries, which are no longer referenced. To have multiple entropy decodes in flight, the EntropyContext is renamed in the same fashion as the pipeline buffers shown in Listing 1.

To maintain the dependencies shown in Figure 2, the entropy\_decode\_line\_task has several annotated arguments. The EntropyContext is annotated with inout to enforce that the lines of each picture are decoded sequentially. H264Mb \*mb\_in is annotated as an input and H264Mb \*mb\_out is annotated as an output, to maintain the dependencies between frames. By passing the pointers to the first H264Mb of the colocated line in the previous entropy buffer and the

# Listing 2. Code fragment replacing the entropy task to perform parallel entropy decoding.

first H264Mb of the current line in the current entropy buffer to mb\_in and mb\_out, respectively, it is ensured that each line x in frame n is decoded before starting to decode line x in frame n+1. A task for each macroblock line is created instead for each macroblock to increase the task granularity at expense of parallelism. The parallelism is still sufficient, however, with a maximum of 135 for QFHD resolution videos.

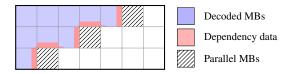

#### 4 Parallelizing Macroblock Reconstruction

In the macroblock reconstruction stage the image is reconstructed using the syntax elements produced by the entropy decoding stage. To reconstruct a macroblock in H.264 several pixel areas from adjacent reconstructed macroblock are required. For each hatched macroblock in Figure 3, the adjacent red pixels are needed for the intra-prediction and the deblocking filter kernels. Therefore, only macroblocks on a wavefront are parallel. The wavefront parallelism is not massive, but sufficient with a maximum of 120 free macroblocks in  $4k \times 2k$  resolution videos. The wavefront parallelism can be exploited using the code fragment in Listing 3.

The wavefront dependencies are static and are covered by the dependencies to the left macroblock and the upper right macroblock. The wavefront dependencies of the reconstruct\_mb\_task are maintained through its H264mb\*arguments by annotating the left macroblock *ml* and upper right macroblock *mur* as inputs and the current macroblock *m* as inout. Since the reconstruct\_mb\_tasks are added in scan line order, this input and the output specification ensures that the wave-

Figure 3. Wavefront parallelism in H.264 macroblock reconstruction.

```

#pragma omp task input(*rc, *s, *ml, *mur) inout(*m

void reconstruct_mb_task(MBRecContext *rc, Slice *s

H264mb *ml, H264mb *mur, H264mb *m);

#pragma omp task inout(*rc) input(*s, mbs[0;rows

*colsl)

output(*pic)

void reconstruct_task (MBRecContext *rc, Slice *s,

H264Mb *mbs, Picture *pic) {

init_ref_list(s);

get_picture_buffer(rc, s);

for(int i=0; i< rows; i++) {</pre>

for (int j=0; j < cols; j++) {

H264mb *m = &mbs[i*cols + j];

H264mb *ml = m - ((j > 0) ? 1: 0);

H264mb *mur = m - (((j < cols-1) && (i > 0))

? cols-1: 0);

reconstruct_mb_task(rc, s, ml, mur, m);

H264mb *lastmb = &mbs[smb_width*smb_height -1];

#pragma omp taskwait on (*lastmb)

release ref(rc, s);

*pic = s->pic;

```

Listing 3. Wavefront algorithm expressed in OmpSs.

front dependencies are maintained. In addition to the pragmas, only the code that computes the left and upper right macroblock must be added to the sequential code. The ability to express dependencies between tasks makes the OmpSs implementation relatively clean and simple.

#### 5 Optimizing Task Granularity

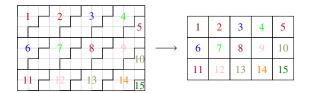

The OmpSs implementation of parallel macroblock reconstruction shown in Listing 3 is a clean way to express the wavefront parallelism. The decode\_mb\_tasks, however, are fine-grained and have an average execution time of around  $2\mu s$  on a commodity processor. The task management overhead of OmpSs does not allow such fine-grained tasks to perform well. A technique to overcome this is to coarsen the tasks by grouping several macroblocks. Due to the wavefront dependencies, however, macroblocks must be grouped in tetris-block shapes, as shown in Figure 4.

Expressing task dependencies between these tetrisshaped superblocks directly is not straightforward, especially when it is desired to support an arbitrary picture and superblock sizes. To overcome this the superblocks are remapped to a regular structure. Independent of their shapes, all superblock variants still exhibit wavefront dependencies. The dependencies can be easily checked, in the same way as the regular ungrouped macroblocks when they are remapped to a regular matrix form as depicted in Figure 4.

Figure 4. Remapping the irregular superblock shapes back to regular shapes simplifies the dependency expression for the programmer and task dependence checking for the runtime system.

The remapping does somewhat increase the code complexity. First, it must be calculated how many superblocks fit in the width and the height of a picture. Second, when decoding the superblock it must be checked which macroblocks belong to this particular superblock. This can be performed by checking if the macroblocks covered by the superblock shape are inside the picture.

If it is ensured that every first superblock in a line has the maximum number of macroblocks in its top row, as is the case in Figure 4, then the code fragment in Listing 4 can be used instead of the code fragment in Listing 3 to reconstruct coarsened superblocks instead of individual macroblocks, for an arbitrary block and picture size.

The code in Listing 4 resembles the code in Listing 3. The main differences are the reduced loop boundaries smb\_rows and smb\_columns, calling the reconstruct\_super\_mb\_task, and checking for valid macroblocks covered by the superblock before calling the inner reconstruct\_mb function. This method is generally applicable to specify coarsened wavefront parallelism in OmpSs for arbitrary superblock sizes and picture dimensions with minimal runtime dependency checking overhead.

#### 6 Experimental Results

A 4-socket cc-NUMA machine with a total of 32 cores is used for the performance evaluation. The full hardware and software specification of our evaluation platform is listed in Table 1.

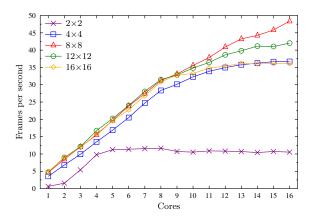

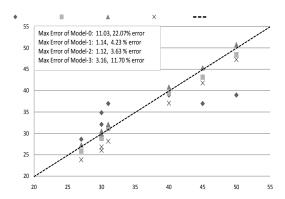

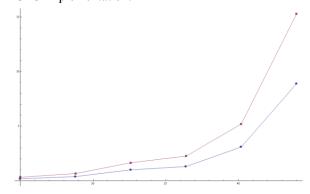

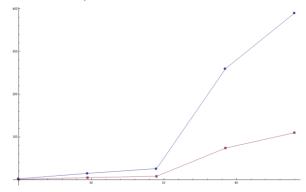

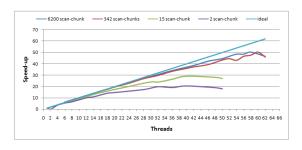

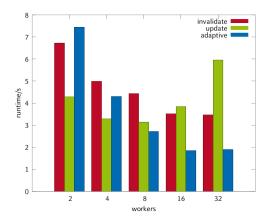

Figure 5 shows the effect of increasing the task granularity described in the previous section. From the figure we can see that the highest performance is achieved with a superblock size of  $8\times8$ . When the task size is too small the performance is bottlenecked

```

#pragma omp task input(*rc, *s, *ml, *mur) inout(*m

void reconstruct_super_mb_task(MBRecContext *rc,

Slice *s, Supermb *ml, Supermb *mur, Supermb *m) {

for (int k=0, i=mby; i< m->mby + sheight; i++, k

for (int j= m->mbx -k ; j< m->mbx- k + swidth;

j++) {

// if (i,j) is a valid macroblock

if (i< rows && j>=0 && j<columns)

reconstruct_mb(rc, s, i, j);

#pragma omp task inout(*rc) input(*s,

smbs[0;srows*scols]) output(*pic)

void reconstruct_task(MBRecContext *rc, Slice *s,

Supermb *smbs, Picture *pic) {

init_ref_list(s);

get picture buffer(rc, s);

for(int i=0; i< srows; i++)

for(int j=0; j< scols; j++) {</pre>

Supermb *m = &smbs[i*scols + j];

Supermb *ml = m - ((j > 0) ? 1: 0);

Supermb *mur = m - (((j < scols-1) && (i > 0))

scols-1: 0);

reconstruct_super_mb_task(rc, s, ml, mur, m);

Supermb *lastmb = &smbs[srows*scols -1];

#pragma omp taskwait on (*lastmb)

release ref(rc, s);

*pic = s->pic;

```

Listing 4. Decoding tetrisshaped superblocks instead of single macroblocks.

| Hardv            | vare       | Software   |              |  |

|------------------|------------|------------|--------------|--|

| Processor        | Xeon X7550 | OS         | Ubuntu 10.10 |  |

| Cores            | 8          | Kernel     | 2.6.35.10    |  |

| Frequency        | 2.00 GHz   | Compiler   | GCC 4.4.5    |  |

| Last level cache | 18 MB      | OmpSs      | Mercurium    |  |

| Sockets          | 4          | compiler   | (git Aug'11) |  |

| Total cores      | 32         | OmpSs      | Nanos++ (git |  |

| Total memory     | 1 TiB      | runtime    | Aug'11)      |  |

| Total mem. BW    | 102.3 GB/s | Opt. level | -O2          |  |

| SMT              | Disabled   |            |              |  |

| Turbo mode       | Disabled   | 1          |              |  |

Table 1. Experimental setup.

by the runtime dependence checking. Increasing the block size from  $2\times 2$  to  $4\times 4$  improves the performance almost proportional to the increase in block size. Too large block sizes, on the other hand show again lower performance, because the parallelism is reduced too much.

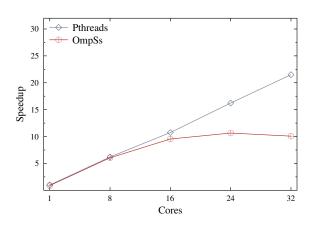

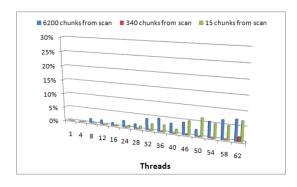

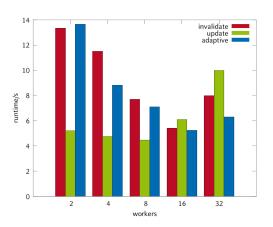

The performance of the OmpSs H.264 decoder is comparing to an optimized Pthreads implementation [1] for up to 32 cores in Figure 6. For the OmpSs variant a block size of  $8\times 8$  is used. The figure shows that the performance results of the two are similar up to 8 cores, but are drifting further apart at higher core counts. By grouping the macroblocks, however, the parallelism is limited, which in turn limits the performance at higher core counts. In the Pthreads version of h264dec the synchronization is highly optimized us-

Figure 5. Performance impact of the different superblock sizes.

ing a line decoding strategy and, therefore, grouping of tasks is not necessary, resulting in a higher scalability.

Figure 6. Speedup results for an optimized Pthreads and OmpSs variant of the full H.264 decoder

To improve the scalability more parallelism can be exploited by starting to decode the next frame before the current frame is completely decoded. Because the motion vectors have limited sizes some macroblocks of the next frame can already be decoded. The difficulty is that another dependency must be added between macroblocks in consecutive frames, which could increase the task dependence checking overhead more than the additional parallelism gains in performance. Another way to increase the scalability is to reduce the task dependency checking overhead. This can be achieved by changing the order tasks are submitted, in order to reduce the tasks-in-flight without reducing the parallel schedulable tasks. Less tasks-in-flight lead to a lowere cost for task dependency checking.

#### 7 Conclusions

In this report we have discussed how H.264 decoding can be parallelized in OmpSs to capture both the function-level and data-level parallelism. In OmpSs this can be done intuitively in contrast to Pthreads and other task-based programming models such as Cilk++ and OpenMP. The runtime task overhead, however, forces that the granularity of the tasks is increased, which reduces the scalability at higher core counts. In future work we will investigate how parallelism can be exploited in consecutive frames. Also we will try to reduce the task dependence checking overhead by reducing the task window size for a given amount of parallelism.

#### 8 Acknowledgements

This research has been supported by the European Community's Seventh Framework Programme [FP7/2007-2013] under the ENCORE Project (www.encore-project.eu), grant agreement  $n^{\circ}$  248647 [4]. Computational support has been provided by the Future SOC Lab of Hasso-Plattner-Institute Potsdam [5].

#### References

- C. C. Chi and B. Juurlink. A QHD-Capable Parallel H.264 Decoder. In *Proc. 25th Int. Conf. on Supercomputing*, 2011.

- [2] L. Dagum and R. Menon. OpenMP: A Proposed Industry Standard API for Shared Memory Programming. *IEEE Computing in Science and Engineering*, 1997.

- [3] A. Duran, E. Ayguadé, R. M. Badia, J. Labarta, L. Martinell, X. Martorell, and J. Planas. OmpSs: A Proposal for Programming Heterogeneous Multi-Core Architectures. *Parallel Processing Letters*, 21, 2011.

- [4] Encore Project. ENabling technologies for a future many-CORE.

- [5] Hasso-Plattner-Institut Potsdam. Future SOC Lab. http://www.hpi.uni-potsdam.de/forschung/future\_soc\_lab.html.

- [6] A. Pop and A. Cohen. A Stream-Computing Extension to OpenMP. In Proc. 6th Int. Conf. on High Performance and Embedded Architectures and Compilers, 2011

- [7] K. H. Randall. Cilk: Efficient Multithreaded Computing. PhD thesis, Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, 1998.

- [8] H. Vandierendonck, P. Pratikakis, and D. Nikolopoulos. Parallel Programming of General-Purpose Programs Using Task-Based Programming Models. In Proc. 3rd USENIX Workshop on Hot Topics in Parallelism, 2011.

## **Service-Based 3D Rendering and Interactive 3D Visualization**

Benjamin Hagedorn Hasso-Plattner-Institut Prof.-Dr.-Helmert-Str. 2-3 D-14482 Potsdam benjamin.hagedorn@hpi.uni-potsdam.de Jürgen Döllner Hasso-Plattner-Institut Prof.-Dr.-Helmert-Str. 2-3 D-14482 Potsdam doellner@hpi.uni-potsdam.de

#### **Abstract**

This report describes the subject and preliminary results of our work in the context of the HPI Future SOC Lab, which generally aims on how to exploit high performance computing (HPC) capabilities for service-based 3D rendering and service-based, interactive 3D visualization. A major focus is on the application of HPC technologies for the creation, management, analysis, and visualization of and interaction with virtual 3D environments, especially with complex 3D city models.

#### 1 Motivation

Virtual 3D city models represent a major type of virtual 3D environments. They can be defined as a digital, geo-referenced representation of spatial objects, structures and phenomena of a distinct geographical area; its components are specified by geometrical, topological, graphical and semantically data and in different levels of detail.

Virtual 3D city models are, e.g., composed of digital terrain models, aerial images, building models, vegetation models, and city furniture models. In general, virtual 3D city models serve as information models that can be used for 3D presentation, 3D analysis, and 3D simulation. Today, virtual 3D city models are used, e.g., for urban planning, mobile network planning, noise pollution mapping, disaster management, or 3D car and pedestrian navigation.

In general, virtual 3D city models represent prominent media for the communication of complex spatial data and situations, as they seamlessly integrate heterogeneous spatial information in a common reference frame and also serve as an innovative, effective user interface. Based on this, virtual 3D city models, as integration platforms for spatial information, represent essential building blocks of today's and future information infrastructures.

#### 1.1 Complexity of 3D city models

Virtual 3D city models are inherently complex in multiple dimensions, e.g., semantics, geometry, ap-

pearance, and storage. Major complexities are described in the following:

Massive amounts of data: Virtual 3D city models typically include massive amounts of image data (e.g., aerial images and façade images) as well as massive amounts of geometry data (e.g., large number of simple building models, or smaller number of buildings modeled in high detail). Vegetation models represent another source of massive data size; a single tree model could contain, e.g., approximately 150,000 polygons).

**Distributed resources:** In today's so called geospatial data infrastructures (GDIs), the different components (i.e., base data) of virtual 3D city models as well as functionalities to access, and process (e.g., analyze) virtual 3D city models can be distributed over the Internet. In specific use cases such as in emergency response scenarios, they need to be identified, assembled, and accessed in an ad-hoc manner.

**Heterogeneity:** Virtual 3D city models are inherently heterogeneous, e.g., in syntax (file formats), schemas (description models), and semantics (conceptual models).

As an example, the virtual 3D city model of Berlin contains about 550,000 building models in moderate and/or high detail, textured with more than 3 million single (real-world) façade textures. The aerial image of Berlin (covering an area of around 850 km2) has a data size of 250 GB. Together with additional thematic data (public transport data, land value data, solar potential) the total size of the virtual 3D city model of Berlin is about 700 GB.

#### 1.2 Service-based approach

The various complexities of virtual 3D city models have an impact on their creation, analysis, publishing, and usage. Our overall approach to tackle these complexities and to cope with these challenges is to design and develop a distributed 3D geovisualization system as a technical framework for 3D geodata integration, analysis, and usage. For this, we apply and combine principles from Service-Oriented Computing (SOC), general principles from 3D visualiza-

tion systems, and standards of the Open Geospatial Consortium (OGC).

Figure 1: 3D client for exploring the 3D city model of Berlin, running on an iPod.

To make complex 3D city models available even for small devices (e.g., smart phones, tablets), we have developed a client/server-system that is based on server-side management and 3D rendering [1]: A portrayal server is hosting a 3D city model in a preprocessed form that is optimized for rendering, synthesizes images of 3D views of this data, and transfers these images to a client, which (in the simplest case) only displays these images. By this, the 3D client is decoupled from the complexity of the underlying 3D geodata. Also, we can optimize data structures, algorithms and rendering techniques with respect to specialized software and hardware for 3D geodata management and 3D rendering at the serverside. - Figure 1 shows our 3D client running on an iPod; it allows a user to interactively explore the virtual 3D city model of Berlin.

Our project in the context of the HPI Future SOC Lab aims on research and development of how to exploit its capabilities for such a distributed 3D visualization

system, especially for 3D geodata preprocessing, analysis, and visualization. The capabilities of interest include the availability of many cores, large mainmemory, GPGPU-based computing, and parallel rendering.

#### 2 Processing massive 3D city models

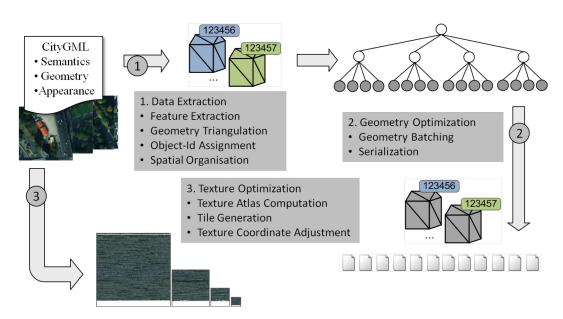

As raw geodata cannot be used directly for visualization and rendering purposes, this data needs to be transformed into graphics representations that can be rendered by a 3D rendering engine. Geodata preparation includes preprocessing of terrain data (geometry and textures, e.g., aerial images) as well as preprocessing of building data (geometry and façade textures). Building data are, e.g., originally provided in the CityGML format, an XML-based standard model and format for the specification of 3D city models, including semantics, geometry, attributes, and appearance information. Figure 2 illustrates the preprocessing of such CityGML building data, which includes the following three major stages and sub tasks:

**Data extraction:** building feature extraction, geometry extraction and triangulation, object-id assignment to each building object, spatial organization of all buildings in a quadtree structure.

**Geometry optimization:** geometry batching, data serialization.

Façade texture optimization: texture atlas computation, texture atlas tiling, texture coordinate adjustment

Typically, the texture data of a large virtual 3D city model does not completely fit into a graphics card's texture memory. Thus, rendering large 3D city models requires selecting and loading the data (in appropriate level of detail) that is required for a specific camera position and view frustum. Texture preprocessing and optimization is a time-consuming stage

Figure 2: Preprocessing scheme for 3D geodata for 3D rendering.

in the preparation of massive 3D building data for efficient rendering and visualization. It includes a) arranging many single façade textures in texture atlases which represent parts of a very large virtual texture and b) cutting these texture atlases into even smaller parts that could be selected and handed over to the graphics card to render a specific view.

Our original implementation of this texture preprocessing stage was designed for being executed on standard desktop PCs. Due to relatively small main memory and disk space (compared to HPC servers), it had to encode and store intermediate texture data as image files on the hard disk. Starting with this implementation we experimented to take advantage of the HPC servers of the HPI Future SOC Lab to reduce the time for texture preprocessing.

First experiments included to reduce I/O-related overhead of this process. For this, we set up and used a 160 GB large virtual RAM drive in the server's main memory. Only through this, we extremely reduced the time to preprocess the massive 3D city model of Berlin (ca. 550.000 buildings including façade textures) from more than a week on a desktop PC (2.80 GHz, 8 logical cores; 6 GB main memory) to less than 15 hours on the Future SOC Lab's RX600-S5-1 (256 GB RAM; 48 logical cores).

Also, we redesigned the implementation of our preprocessing tools to take advantage of potentially very large main memory (for storing intermediate texture data instead of encoding it and writing to hard disk) and large number of available threads (for increasing the degree of parallel tiling of texture atlases).

#### 3 Processing massive 3D point clouds

3D point clouds are another major source of 3D geodata, which are collected, e.g., via airborne or terrestrial laser scanning. 3D point clouds can represent a digital surface model of the earth's surface and are a starting point for deriving high-level data, e.g., based on classification, filtering, and reconstruction algorithms. For such algorithms it is crucial to be able to handle and manage the often very large 3D point data sets. 3D point clouds of a single city can easily contain several billion points. In the past, we had developed a set of algorithms and tools to cope with this challenge and to process, analyze, and visualize massive 3D point clouds [2, 3].

Spatial organization and rasterization are two major preprocessing tasks for 3D point clouds:

**Spatial organization:** To efficiently access and spatially analyze 3D points, they need to be ordered in a way that allows efficient access to the data; quadtrees and octrees represent common structures for their organization.

**Rasterization:** Rasterized 3D point clouds are a central component for visualization techniques and processing algorithms, as they allow efficient access

to points within a specific bounding box. Rasterization transforms arbitrary distributed 3D points into a gridded, reduced, and consolidated representation; representative points are selected and missing points are computed and complemented. Rasterized point clouds are used, e.g., for the computation of triangulated surface models, for consistent level-of-detail techniques, and other efficient processing algorithms.

In the context of the Future SOC Lab we have started to research on how the HPC capabilities can help to improve speed and quality of these two tasks.

#### 3.1 Spatially organizing 3D point clouds

To create a quadtree/octree structure, we have used the PARTREE algorithm, a parallel algorithm that creates several trees that are combined to a single one later (Figure 3).

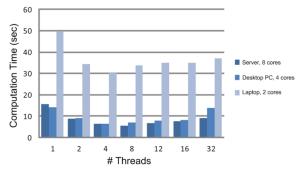

The parallel quadtree/octree generation process for 3D point clouds was implemented based on OpenMP. We tested our implementation with data sets of up to 26.4 million 3D points. In this setting, the HPC system with 8 logical cores (FluiDyna Typhoon, 2.4 GHz, 24 GB RAM, 8 logical cores) was faster than a Desktop PC with 4 logical cores; however, the gain in time is not dramatically (Figure 4). The time required to merge the generated component trees into one tree is increasing with their number (i.e., the number of threads); in this step, the HPC server outperforms the desktop system.

Figure 3: Functional scheme of PARTREE algorithm. Two threads create two local trees (here: quadtrees) that are merged then into a single one.

Figure 4: Time to compute an octree from 26.4 million 3D points by PARTREE method.

#### 3.2 Rasterization of 3D point clouds

Rasterization is a multi-step process which 1) identifies for each point of an unordered 3D point cloud the corresponding raster cell and assigns the raster cell ID, 2) ordering the points according to their raster cell ID, 3) computing one characteristic 3D point for each raster cell (representing the relevant input points), and 4) interpolating cell points for empty raster cells. For sorting the points according to their raster cell ID, our implementation uses the Bitonicsort algorithm, which requires to establish a bitonic order before sorting.

We have implemented the rasterization algorithm in two versions: a) a version for multi-core processors (using OpenMP) and b) a data-parallel GPU-based version (using CUDA). The CUDA version has been tested with the Future SOC Lab's TESLA system. It can rasterize a point cloud of 30.5 million 3D points in only 22 minutes in contrast to more than 5 hours of a single threaded CPU-version.

#### 4 Next Steps

The continuation of our work in the area of exploitation of HPC capabilities for service-based 3D rendering and 3D visualization systems and in the context of the HPI Future SOC Lab will include further improvement of our algorithms, processes, and tools. Also, we plan to extend our work to research and development on HPC-based analysis of massive 3D geodata (such as solar potential analysis) and on service-based technologies for assisted interaction and camera control in massive virtual 3D city models [4]. For this, we will exploit parallel and GPU-based algorithms to generate so called "best views" on virtual 3D city models based on visual, geometrical and usage-related characteristics.

#### 5 Conclusions

This report briefly described the subject of our research and development in the context of the HPI future SOC Lab, preliminary results, as well as intended future work. Work and results were mainly in the areas of preprocessing massive 3D city model data and processing of massive 3D point clouds. Here, we could dramatically increase the time required to preprocess raw 3D geodata (CityGML data with geometry and textures; and massive 3D point clouds). Also, we identified additional opportunities for optimizing these algorithms. More generally, this work leads to new opportunities for research and development on advanced and innovative technologies for the exploitation (e.g., analysis and visualization) of massive spatial 3D data sets.

#### Acknowledgment

We would like to thank Markus Behrens for his help with the implementation and evaluation of 3D point cloud processing and its evaluation.

#### References

- [1] D. Hildebrandt, J. Klimke, B. Hagedorn, J. Döllner: Service-oriented Interactive 3D Visualization of Massive 3D City Models on Thin Clients. *In: Proc. of 2nd Int. Conf. on Computing for Geospatial Research & Application COM. Geo 2011*, 2011.

- [2] R. Richter, J. Döllner: Out-of-Core Real-Time Visualization of Massive 3D Point Clouds. In: Proc. of 7th Int. Conf. on Virtual Reality, Computer Graphics, Visualisation and Interaction in Africa, pp. 121-128, 2010

- [3] R. Richter, J. Döllner: Potentiale von massiven 3D Punktwolkendatenströmen. *In: Proc. of Geoinformatik* 2012, Braunschweig, 2012.

- [4] J. Klimke, B. Hagedorn, J. Döllner: A Service-based Concept for Camera Control in 3D Geovirtual Environments. *In: Proc. of 7th Int. 3D GeoInfo Conference* 2012. (accepted)

## Future SOC Lab Autumn Term Project Activities Report: Benchmarking and Tenant Placement for Efficient Cloud Operations

Multi-Tenancy Project Team SAP Innovation Center Potsdam Prof.-Dr.-Helmert-Str. 2-3 14482 Potsdam, Germany Jan Schaffner EPIC Chair, Hasso-Plattner-Institute August-Bebel-Straße 88 14482 Potsdam, Germany

#### **Abstract**

Cloud computing mainly turns the overall IT costs of companies that move into the cloud into operational expenditures that they pay for the consumed services to a cloud provider. Consequently, the risk of correctly dimensioning the infrastructure as well as the need to keep capital expenditures as well as administrative costs at viable levels is transferred to the cloud provider. Multi-tenancy, i.e. consolidating several customers onto the same infrastructure, is one method to achieve higher utilization and therefore a more efficient cloud operation.

This project's main focus is on the efficiency and reliability of cloud services provided by server machines in virtualized, multi-tenant environments. By intelligently placing and later migrating tenants in this environment, we aim to achieve load balancing and a consistent service quality of the provided cloud services while keeping operational costs minimal. Before these investigations can take place, an evaluation and testing environment must be built up and suitable testing scenarios, e.g. in the form of benchmarks, need to be defined. This was the first major work stream that we followed out in the past lab term. The second work stream relates to tenant placement. Both are work-in-progress and are concisely described in the following. A proposal for continuation of this project in the coming lab term concludes this report.

#### 1 Introduction

Having instantaneous access to relevant business information anywhere and anytime is becoming more and more important [1]. To realize this economically, it is necessary to deal with huge amounts of data and load at fewer costs. Big companies that felt this pres-

sure like Amazon [2] and Google [3] developed approaches to handle these requirements that are now called Cloud Computing.

The idea behind the cloud is to offer computing as a service with seemingly endless capacity that can be added or removed on demand [4]. The user keeps the data inside the cloud infrastructure and has access to the performance of a data center to execute complex operations on it. Through the network, data can be accessed in an easy way with various devices.

One essential aspect to achieve the required cost savings is multi-tenancy [4], which describes consolidating multiple clients on a small hardware set. An additional advantage is that clients can not only share the server hardware, but also applications, content and data

When thinking about multi-tenancy, several challenges become obvious [5, 6], such as tenant placement and tenant migration. Another very important topic is benchmarking. It is not enough to develop new technologies, but also to demonstrate where exactly the strengths of a system are and how it performs compared to others. Furthermore, there is a need to support the development process with tools that can help checking the quality of the implemented approach. To do this, benchmarks can be helpful tool.

#### 2 Benchmarking

Current database benchmarks do not support cloud computing scenarios and multi-tenancy. To realize this, the following tasks have to be tackled:

- handling of data sizes and user scenarios that are typical for cloud computing

- supporting multi-tenant environments

- defining an industry benchmark to compare different approaches

The goal of this first work stream is to implement a first benchmark that fits the needs described above. Our approach is guided through the reuse of the already existing database benchmark called Composite Benchmark for Transactions and Reporting (CBTR) [7] developed by Anja Bog at the EPIC chair of HPI.

This system brings in several useful functionalities compared to other database benchmarks. It provides the possibility to mix analytical and transactional workloads and it operates on a dataset based on real customer data. Furthermore, it uses the Order-to-Cash scenario with a schema definition typical for SAP customers, namely implementing several tables with more than 100 columns.

The original implementation can handle one tenant that maintains the connection to the database. This tenant serves several clients that continuously query the database, to identify its properties under maximum load. This scenario had to be extended to a multi-tenant system with variable load profiles and think times.

Based on the original CBTR implementation we conducted an extension of the existing architecture as well as implemented new functionalities to support multiple tenants. We call the resulting Benchmark CBTRmt.

The following functionalities are part of CBTRmt:

- Maintaining multiple tenants at the same time, where each of them handles a number of different clients.

- Maintaining connection pooling for each of the tenants.

- Configurable think times between the queries submitted by each client.

- A load profile that specifies the workload of each tenant on the base of a 24h day.

- Exchangeable tenants.

While developing the described benchmark, the need to create an arbitrary number of tenants with different sizes, loads and datasets became apparent. The so-called Experiment Generator (ExpG) was therefore conceptualized to be able to create all necessary files and setting for a complete experiment setup.

The functionality covered by the ExpG includes the generation of realistic data sets for the database schema used in the CBTR benchmark. The implementation not only considers the data type, length, primary key and foreign key specifications, but also the size relation between the input tables. In parallel to the data generation, also query parameters are generated. This allows the querying of the generated data, just as it would be the original customer data. The ExpG is implemented in Java, based on a randomization algorithm. By specifying the seed of the Random object, one can influence the data generation

directly. It is also possible to regenerate an old dataset by knowing its seed value.

One open issue for the ExpG is the support of different database schemas, which is already planned for the upcoming project phase. The output of the ExpG can then be directly loaded into the CBTRmt Benchmark and run as a whole experiment on the database.

This work stream heavily employed the SAP HANA machine in the Future SOC Lab as well as one to two high-performance servers to generate the tenant load on the SAP HANA machine as client machines.

#### 3 Tenant Placement

The second work stream focuses on the Robust Tenant Placement and Migration Problem (RTP). The goal of this optimization problem is to assign  $r \ge 2$  copies of a given number of tenants to a number of (cloud) servers such that

- no server is overloaded in terms of memory and CPU,

- no server contains more than one copy per tenant,

- the failure of a single server does not cause overloading any other server, and

- the number of active servers is minimal.

A tenant comprises a set of database tables as well as users issuing requests against those tables. Any tenant t is characterized by its size  $\sigma(t)$  (i.e. the amount of main memory each replica of the tenant consumes) and its load l(t). For in-memory column databases, the latter depends on the current request rates of the tenant's users as well as the size of a tenant. For more information about how to experimentally obtain l(t) for a given set of database tables and workload, we refer to our previous work on performance prediction for in-memory column databases [9]. Note that we assume that l(t) is additive across multiple tenants. We assume that queries are load balanced across tenant replicas in a round-robin fashion. Thus, a server only receives a fraction of the total load of a tenant, depending on the number of replicas.

Tenants are placed on servers. We call a server active if the server holds at least one tenant with non-zero size and non-zero load.

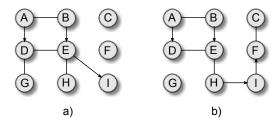

**Example 1.** Figure 1 (left) depicts an exemplary placement. Tenants A, B, C, D, E each have two copies and are distributed on four servers S1–S4. Each server has load capacity lcap = 1.0 and memory is limit-less ( $\sigma cap = \infty$ ). The load consumption of the tenants are depicted as small numbers in the boxes. The total load of a tenant is split across all its replicas (e.g. the total load of tenant A is 0.2). The failure of a server, say server S2, means that server S4 must in

turn handle the load that was formerly shared between servers S2 and S4. This must not lead to the overload of S4. In this example, S4 gets a load of 0.3 after failure of S2, which does not lead to overloading server S4.

Figure 1: Left: Greedy-Placement and Mirroring. Right: Interleaving

At first glance, RTP resembles the twodimensional bin- packing with conflicts, where the conflicts arise from the constraint that no server should hold more than one copy of the same tenant.

However, RTP is different from the twodimensional bin-packing [8] with conflicts [9] problem because we are interested in finding an assignment of tenants to servers such that the assignment is robust towards server failures. A server failure causes a load increase on those servers that hold copies of tenants that were placed on the failed server. This excess load is shared among the remaining servers that hold replicas of those tenants. While it is common to handle replication using a static placement strategy (e.g. mirroring), we let the tenant placement be flexible within the following constraints: tenants can be placed on arbitrary servers, as long as no two copies of any particular tenant reside on the same server; and, each server must have enough spare capacity to deal with extra load coming from tenants on a failed servers. As a result of allowing a flexible placement strategy, assignments with fewer active servers can often be found, as we shall see in the following example.

**Example 2.** Fig. 1 (right) shows an example with five tenants, A, B, C, D, and E, as well as their load l(t) (we neglect  $\sigma(t)$  in this example). A conventional approach to assigning those tenants to servers would be to sort the tenants by load (in descending order), use a simple greedy algorithm assuming only one copy per tenant must be placed, and finally mirroring the resulting placement. This approach, shown on the left side of the figure, requires four servers. A flexible way to place the same tenants, which we shall call interleaving, shown on the right side of the figure, requires only three servers. Table 1 shows the total load on each server both for normal operations and with one other server failing. For example, in the

mirrored case, a failure of server S1 doubles the load on S3, while the load on S2 and S4 remains constant. With interleaving, the excess load caused by a failure is distributed among multiple servers.

In addition to guaranteeing that placements are robust towards single-server failures, we acknowledge that dealing with a variable number of servers requires frequent migration of tenant replicas between servers. RTP is an incremental problem in the sense that it has to be solved periodically using an existing placement as a starting point. The frequency of the reassignment interval limits the amount of change that can be applied to the original placement. In previous work we have found that migrating tenants away from or onto an active server temporarily reduces the server's ability to serve requests [10]. In the case of in-memory column databases, we are able to precisely quantify the reduction of a servers query processing capacity lcap incurred by migration for a given set of database tables and workload. The size of a tenant does not impact how much the capacity of a server is reduced during migration but it affects how long it takes to migrate the tenant [10]. Thus, the amount of migration that is permissible in each step depends on the length of the reorganization interval and to what degree migrations can be performed in parallel.

Currently, we are conducting experiments on a variety of algorithmic approaches to solve the RTP as well as experiments for finding a good benchmark. Algorithms we evaluate on the Future SOC Lab computing resources range from special purpose greedy-heuristics to meta-heuristics and, finally, exact algorithms. Our experiments are work-in-progress.

#### 4 Project Proposal for Next Lab Term

As both work streams are still work-in-progress we propose a continuation of the current project also in the Future SOC Lab spring term of 2012. We plan to apply current implementations and findings in order to achieve the defined goals. The focus remains on efficiency and reliability of cloud services provided by server machines in virtualized, multi-tenant environments. By migrating tenants in this environment, we aim to achieve load balancing and a consistent service quality of the provided cloud services.

A migration manager responsible for this process shall act as follows: First, a forecasting method estimates the load that tenants are likely to produce. This forecast could be based on load profiles of customers as well as business information such as a factory calendar. Based on this forecast, a multi-criteria optimization takes place. Examples for objectives in the optimization could be cost of the migration process

and possible re-migration, benefit of load balancing and expected quality of service.

Success will be evaluated based on fulfillment of given service level agreements in experiments based on real-world scenario as well as on other criteria that will be defined as part of this project. In a next step we plan to extend the approach to include failure prediction algorithms for migration decision-making once a potential failure has been identified. This aims at increasing the reliability of the overall cloud solution for cases in which server machines may fail. These activities would make use of the FutureSOC Lab computing resources in a similar way as in the first project phase.

#### 5 Acknowledgements

The project members wish to thank Bernhard Rabe of Future SOC Lab/HPI for his invaluable administra-tive support to setup and run the numerous tests as part of the benchmarking efforts.

#### 6 References

- [1] Shuai Zhang, Shufen Zhang, Xuebin Chen, Xiuzhen Huo. *Cloud Computing Research and Development Trend*. Future Networks, International Conference on, pp. 93-97, 2010 Second International Conference on Future Networks, 2010.

- [2] Amazon Elastic Compute Cloud [URL]. http://aws.amazon.com/ec2/, access on Feb. 2012.

- [3] Google App Engine [URL]. http://code.google.com/appengine/, access on Feb. 2012.

- [4] Peter Mell, Timothy Grance. The NIST Definition of the Cloud Computing. NIST Special Publication 800-145, 2011.

- [5] Curino, Carlo et al. Relational Cloud: A Databaseas-a-Service for the Cloud. 5th Biennial Conference on Innovative Data Systems Research, CIDR 2011, January 9-12, 2011 Asilomar, California.

- [6] Dean Jacobs, Stefan Aulbach. Ruminations on Multi-Tenant Databases. BTW 2007: 514-521

- [7] Anja Bog, Hasso Plattner, Alexander Zeier. A mixed transaction processing and operational reporting benchmark. Springer Science + Business Media, LLC 2010.

- [8] W. Leinberger, G. Karypis, and V. Kumar. Multi-Capacity Bin Packing Algorithms with Applications to Job Scheduling under Multiple Constraints. In ICPP, pages 404–412, 1999.

- [9] L. Epstein and A. Levin. On Bin Packing with Conflicts. SIAM Journal on Optimization, 19(3):1270– 1298, 2008.

- [10] J. Schaffner, B. Eckart, D. Jacobs, C. Schwarz, H. Plattner, and A. Zeier. *Predicting in-memory data-base performance for automating cluster manage-ment tasks*. In Proceedings of the 27th International Conference on Data Engineering, ICDE 2011, April

11-16, 2011, Hannover, Germany, pages 1264–1275, 2011

## Towards Multi-Core and In-Memory for IDS Alert Correlation: Approaches and Capabilities

Sebastian Roschke, Seraj Fayyad, David Jaeger, Feng Cheng, Christoph Meinel Hasso-Plattner-Institut Prof.-Dr.-Helmert-Str. 2-3 14482 Potsdam

{sebastian.roschke, seraj.fayyad, feng.cheng, meinel}@hpi.uni-potsdam.de {david.jaeger}@student.hpi.uni-potsdam.de

#### **Abstract**

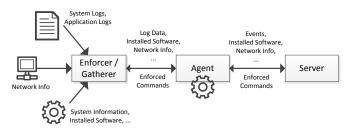

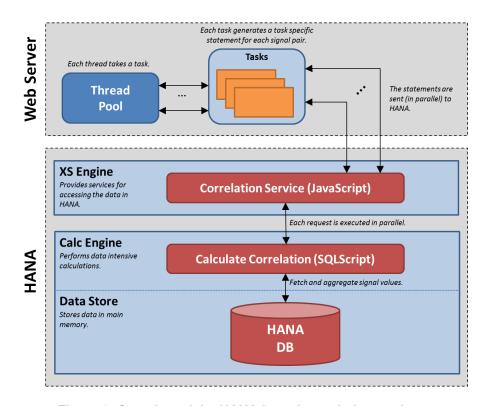

Intrusion Detection Systems (IDS) have been widely deployed in practice for detecting malicious behavior on network communication and hosts. The problem of false-positive alerts is usually addressed by correlation and clustering of alerts. As real-time analysis is crucial for security operators, this process needs to be finished as fast as possible, which is a challenging task as the amount of alerts produced in large scale deployments of distributed IDS is significantly high. We identify the data storage and processing algorithms to be the most important factors influencing the performance of clustering and correlation. The Security Analytics Lab (SAL) is developed to make use of multicore and in-memory processing. Using the SAL, a multitude of algorithms is implemented, such as Attack-Graph based correlation using HMMs, QROCK categorical clustering, and rule-based correlation using a knowledge base. The SAL is using the Common Event Expression (CEE) and supports generic flat log data.

#### 1 Alert Correlation and its Performance

The alert correlation framework usually consists of several components [4]: Normalization, Aggregation (Clustering), Correlation, False Alert Reduction, Attack Strategy Analysis, and Prioritization. Over the last years, alert correlation research focused on new methods and technologies for these components. IDMEF[5], CEE [7] and CVE [6] are important efforts in the field of Normalization. Approaches of aggregation are mostly based on similarity of alerts or generalization hierarchies. The correlation algorithms [4] can be classified as: Scenario-based correlation, Rule-based correlation, Statistical correlation, and Temporal correlation. The aspect of performance and quality is the focus of the "Security Analytics Lab" (SAL) [2]. The SAL is developed to provide an experiment envi-

ronment for IDS correlation algorithms to support security operators with real-time monitoring and forensics. The SAL is designed with efficiency in mind, i.e., optimized quality and performance of the algorithms as well as the storage and organization of original alerts. The platform introduced in [2] considers different storage mechanisms and can handle massive amounts of data for specific algorithms that make heavy use of the caching mechanisms of the platform. For storage, a column-based database, an In-Memory alert storage, and memory-based index tables lead to significant improvements of the performance. Furthermore, the SAL supports the usage of GPU-based algorithms by providing necessary APIs.

We believe that research in the area of IDS and network security as application for multi-core and Inmemory based platforms can provide new paradigms for conducting security. Correlation and clustering is currently only done in a limited way using filtered data sets. Using the multi-core and In-memory platforms, it might be possible to do correlation and clustering on an unfiltered data set. Thus, it might not be necessary to fine tune (e.g., exclude certain detection rules) the IDS sensors anymore, as the correlation and clustering can do meaningful reasoning on all alerts in a short time. Furthermore, we expect correlation and clustering services offered in the Cloud. A flexible and extensible correlation platform can provide the foundation work for a new paradigm in security.

#### 2. Results and Achievements

During the last few month, we have been working on improving the implementation on the Common Event expression (CEE) [7]. Furthermore, we have been implementing several convenience features to improve the handling of the platform in case of multiple data sets. A data set switching mechanism is implemented that allows the switching of data bases from the web UI. To improve the Attack Graph (AG) based correlation, we optimized the modeling of the attack graph

and adjusted the corresponding AG correlation module. The AG-based algorithm was redesigned to fit additional attack scenarios. We further developed an algorithm for evaluating attack paths and attacks progress depending on multiple conditions, such as importance of the target, existence of a public exploit, etc.

Apart from the practical achievements, we have been able to publish a paper on the Attack Graph based algorithm [3], which is currently finalized for a Journal publication. A detailed description of the results is given in the following subsections.

We deployed the prototype of the correlation platform a FutureSOC VM (1 CPU, 4 GB Ram) and developed multiple features to improve performance and usability. Furthermore, we conducted some tests and experiments using the NVIDIA FluiDyna System as well as the Fujitsu RX600 S5 1.

#### 3 Towards High-quality Attack-Graphbased Correlation

In this section, a modified AG based correlation algorithm is described which only creates explicit correlations. Implicit correlations, as described in [14], make it difficult to use the correlated alerts in the graph for forensic analysis of similar attack scenarios. Furthermore, the hardware environment used for the In-Memory databases provides machines with huge amounts of main memory which downgrades the priority of memory efficiency for this work. The algorithms consists of five steps, while each step can be parameterized to fine tune the results: 1) preparation, 2) alert mapping, 3) aggregation of alerts, 4) building of an alert dependency graph, and 5) searching for alert subsets that are related. In the preparation phase, all necessary information is loaded, i.e., the system and network information is gathered, the database with alert classifications is imported, and the AG for the network is loaded. The proposed algorithm works based on the exploit dependency graph created by MulVAL [15]. This type of attack graph is used simply because the tool is freely available. MulVAL is used to generate an AG which describes the corresponding system and network information for the target network. The output of MulVAL is a simple graph description which is not using a standardized format. Thus, the MulVAL output is interpreted and a corresponding graph structure is build in memory.

The algorithm is based on a set of basic definitions.

#### 3.1 Definitions

Let  $\mathcal{T}$  be the set of all timestamps,  $\mathcal{H}$  be the set of possible hosts, and  $\mathcal{C}$  be the set of classifications.  $\mathcal{A}$  can be defined as:

$$\mathcal{A} = \mathcal{T} \times \mathcal{H} \times \mathcal{H} \times \mathcal{C} \tag{1}$$

Let a single alert  $a \in \mathcal{A}$  be a tuple a = (t, s, d, c) while the following functions are defined:

- ts(a) = t returns  $t \in T$ , the timestamp of the alert

- src(a) = s returns  $s \in H$ , the source host of the alerts

- dst(a) = d returns  $d \in H$ , the destination host of the alert

- class(a) = c returns  $c \in C$ , the classification of the alert

Let  $\mathcal{I}$  be the set of impacts described by MulVAL [15] and  $\mathcal{VR}$  be the set of known vulnerabilities. Let V be a set of vertices defined as:

$$V = \mathcal{I} \times \mathcal{H} \times \mathcal{VR} \tag{2}$$

For each triple  $v = (im, h, r) \mid v \in V$ , the following functions are defined:

- imp(v) = im returns  $im \in \mathcal{I}$ , the impact of the vertex

- host(v) = h returns  $h \in \mathcal{H}$ , the host of the vertex

- ref(v) = r returns  $r \in \mathcal{VR}$ , the vulnerability reference of the vertex

Let AG=(V,E) be an AG with vertices V and edges E. An edge  $e \in E \subseteq V^2$  is an ordered tuple of vertices (v,v') with  $v \in V \land v' \in V$ . PAG defines all the paths in the AG. The path  $P \in PAG$  is defined as a set of edges  $P=(v,v') \in E$ . ord(P) defines the number of edges in the path P. in(v,P) depicts whether a vertex lies in the path:

$$in(v, P) := \exists (v, v') \in P \lor \exists (v', v) \in P$$

(3)

#### 3.2 Mapping

The mapping function  $map_i$  maps matching alerts to specific nodes in the AG and is defined as:

$$map_i: a \mapsto \{v \in V \mid \Phi_i(a, v)\} \tag{4}$$

There are different kinds of  $\Phi_i(a, v)$  defined in (5), (6), (7), (8), and (9) to parameterize the mapping function.

$$\Phi_1(a, v) := \exists v' \in V : (src(a) = host(v'))$$

$$\land (dst(a) = host(v))$$

$$\land (class(a) = ref(v))$$

(5)

$$\Phi_2(a,v) := (dst(a) = host(v)) \land (class(a) = ref(v))$$

(6)

Figure 1. AG-based Correlation Algorithm - Mapping

$$\Phi_3(a, v) := (class(a) = ref(v)) \tag{7}$$

$$\Phi_4(a, v) := \exists v' \in V : (src(a) = host(v'))$$

$$\wedge (dst(a) = host(v)) \tag{8}$$

$$\Phi_5(a, v) := (dst(a) = host(v)) \tag{9}$$

In this work, the modes use a specific  $\Phi_i(a, v)$ . The match modes are named as follows:

- $\Phi_1(a, v)$  match mode *cvesrcdst*

- $\Phi_2(a, v)$  match mode *cvedst*

- $\Phi_3(a, v)$  match mode *cve*

- $\Phi_4(a, v)$  match mode *srcdst*

- $\Phi_5(a,v)$  match mode dst

Figure 1 shows the principle of the mapping step. The stream of alerts is mapped to the nodes of the AG, i.e., a filtering is done based on the match mode.

#### 3.3 Aggregation

Let  $A \subset \mathcal{A}$  be the set of alert that is supposed to be aggregated. Let th be a threshold and  $x \in A, y \in A$  two alerts, then the relation  $R_A$  is defined as:

$$R_{A} = \{(x,y) \in A^{2} : (|ts(x) - ts(y)| < th) \land (src(x) = src(y)) \land (dst(x) = dst(y)) \land (class(x) = class(y))\}$$

(10)

$R_A^*$  defines an equivalence relation on the transitive closure of  $R_A$ . The alert aggregation combines alerts that are similar but where created together in a short time, i.e., the difference of the timestamps is below a certain threshold th. It defines a set of equivalence classes  $A_{/R_A^*}$  over the equivalence relation  $R_A^*$ .

#### 3.4 Alert Dependencies

Let  $A_m \subset A$  be the set of alerts that have been matched to a node in an AG:

$$A_m = \{ [a] \in A_{/R_A^*} \mid map_i(a) \neq \emptyset \} \qquad (11)$$

The alert dependencies are represented by a graph  $DG = (A_m, E_{m,k})$ , with  $E_{m,k}$  as defined in (12).

$$E_{m,k} = \{([x], [y]) \in (A_{/R_A^*})^2 \mid \Psi_k([x], [y])\}$$

(12)

The set  $E_{m,k}$  can be parameterized by the functions  $\Psi_k$  as shown in (13), (14), and (15).

$$\Psi_1([x], [y]) := (ts([x]) < ts([y]))$$

$$\wedge (\exists (v, w) \in E : (v \in maps_i(x))$$

$$\wedge w \in maps_i(y))) \qquad (13)$$

$$\Psi_{2}([x], [y]) := (ts([x]) < ts([y]))$$

$$\wedge (\exists P \in PAG : (ord(P) = n))$$

$$\wedge (\exists v, w :$$

$$(v \in maps_{i}(x) \wedge w \in maps_{i}(y))$$

$$\wedge in(v, P) \wedge in(w, P))) \qquad (14)$$

$$\Psi_{3}([x], [y]) := (ts([x]) < ts([y]))$$

$$\wedge (\exists P \in PAG : \exists v, w :$$

$$(v \in maps_{i}(x) \land w \in maps_{i}(y)$$

$$\wedge in(v, P) \land in(w, P))) \qquad (15)$$

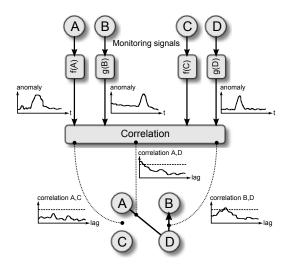

The dependency graph DG is defined by the matched and aggregated alerts  $A_m$  as vertices and the relations between these alerts as edges  $E_{m,k}$ . There are three possible ways to define these relations using  $\Psi_k$ .  $\Psi_1$  defines two alerts as related, if they are mapped to neighboring vertices in AG.  $\Psi_2$  defines two alerts as related, if they are mapped to two vertices in AG that are connected by the path P with the length of n.  $\Psi_3$  defines two alerts as related, if they are mapped to two vertices in AG that are part of the same path P. As shown in Figure 2, the alert dependency graph is created based on the mapping results.

#### 3.5 Searching

Each path in the alert dependency graph DG identifies a subset of alerts that might be part of an attack scenario. DG is used in the last step to determine the most interesting subsets of alerts, respectively the most interesting path in the alert dependency graph. The last step of searching alert subsets is done by performing a Floyd Warshall algorithm [16, 17] to find all

Figure 2. AG-based Correlation Algorithm - Creation

Figure 3. AG-based Correlation Algorithm - Finding

the shortest paths. Furthermore, the diameter dia (i.e. the value of the longest instance of the shortest paths) is determined and each path  $DP_i$  that has the length ord(DP)=dia is converted in subsets of alerts. All the subsets  $S_x$  are defined as:

$$S_x = \{ a \in A \mid in(a, DP_i) \}$$

(16)

Figure 3 shows the identified attack subsets in the dependency graph that correspond to the diameter.

With a simple optimization, the algorithm allows to identify multiple different attack scenarios of the same anatomy. By sorting the suspicious alert subsets according to the smallest difference between alert  $a_1$  and  $a_n$ , the algorithm will identify the alerts that are near each other on the time-line as related to one attack scenario. Let  $as = \{a_1, ..., a_n\}$  and  $bs = \{b_1, ..., b_n\}$  be two alert sets where the only difference between  $a_i$  and  $b_i$  is the times-tamp  $ts(a_i) \neq ts(b_i)$ . There are three different combinations how these alerts can be located on a time-line:

- 1. as and bs are not overlapping at all, i.e.,  $ts(a_n) < ts(b_1)$

- 2.  $as = \{a_1, a_2, ..., a_k, ...a_n\}$  and  $bs = \{b_1, ..., b_n\}$  are partially overlapping, i.e.,  $\exists k \in \mathbb{N} \forall a_{i \in \{1, k\}} \mid ts(a_k) > ts(b_1)$

- 3. bs is completely overlapped by as, i.e.,  $(ts(a_1) < ts(b_1)) \land (ts(a_n) > ts(b_n))$

The modified algorithm can identify both suspicious alert sets in case 1. Due to the memory limitation, this algorithm only considers the last matching alert for each node in the AG. The cases 2 and 3 are difficult to be identified correctly.

# 4 Evaluation and Analysis of Attack Graphs

Attack Graphs describe a pre-defined known set of attack scenarios that are existing in the current network under surveillance. These scenarios can be used to match attack steps very closely and to follow an attacker through the network in real-time. Additionally, the different attack paths can be evaluated according to certain severity scores. Thus, having a low severity score on a currently exploited attack path, the security operators might be able to finish more urgent tasks before dealing with this specific attack. Whereas if an attacker is exploiting an attack path that covers very important systems and therefore having a high severity score, the security operators might need to deal with this attack urgently. One example application of the evaluation of the attack paths is the sensor placement. Before data can be monitored and be managed in the SAL, sensors have to be installed in the scenario. These sensors can come in two possible forms, i.e., as host-based IDS (HIDS) or as network-based IDS (NIDS). Each of these forms is suited for the detection of its specific kind of attack. Host-based sensors can be used to monitor unexpected behavior on a specific host while Network-based sensors can be used to monitor unexpected behavior on the network. Our goal is an effective monitoring infrastructure, which only employs a small number of sensors that can detect each possible attack in the scenario. With these conditions and the outlined preferences for the sensors, we can place sensors with the following strategy.

HIDS sensors are the only way to detect local exploits, thus installing a HIDS on all hosts that have at least one locally exploitable vulnerability might be necessary. NIDS on the other hand, can only detect remote exploits but can detect these for multiple hosts, depending on the host they are installed on. In this respect it is necessary to find all possible remote exploits and extract the hosts that are routing the network traffic for these exploits. The severity score can be considered to find an optimal solution according to the scenario. In order to do this, all single step attack paths can be extracted from the attack graph and the network route between the source and target of the attack path can be determined. Eventually, all hosts need to be listed in the network route, except the starting node (e.g. the external network connection), because this one can be considered to be under control of the attacker. Using the set cover algorithm described in [18], a minimal number of hosts can be found, which are able to intercept all remote exploits. Finally, these hosts are directly used for the placement of the NIDS.

#### 5. Future Work

Within the next few months, we want to conduct a few more step to improve the quality of the correlation algorithms deployed on this platform. We would like to work towards our vision with the following practical steps. Setting up a real deployment with multiple sensors to conduct practical experiments might be very useful. Testing the platform with a dataset of 1 TB as well as implementation of more algorithms with multi-core support will prove the applicability of the platform. The implementation of HANA support can provide a performance boost and improves the flexibility of the SAL. An interactive coding module for security operators would provide exploration functionality for data sets. Apart from the implementation requirements, the are multiple research topics, such as research on correlation algorithms that are using environment information and attack graphs, research on statistical correlation algorithms, research on visualization techniques for correlation results, research on prediction of alerts and events, research evaluation of attack paths and attackers, research on prevention techniques, simulation of attack traffic and alerts, as well as research on correlation of log events and corresponding requirements (in contrast to correlation of IDS alerts). We hope that we can open one or two of these new research areas by prolonging the project.

#### References

- [1] S. Roschke, F. Cheng, Ch. Meinel: *Using Vulnerability Information and Attack Graphs for Intrusion Detection* In: Proceedings of 6th International Conference on Information Assurance and Security (IAS'10), IEEE Press, Atlanta, United States, pp. 104-109 (August 2010).

- [2] Roschke, S., Cheng, F., Meinel, Ch.: An Alert Correlation Platform for Memory-Supported Techniques. In: Concurrency and Computation, Wiley Blackwell, 2011 (to appear).

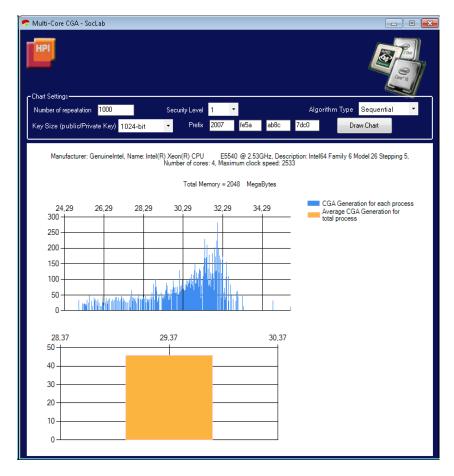

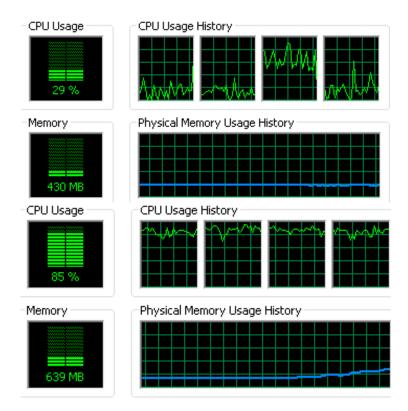

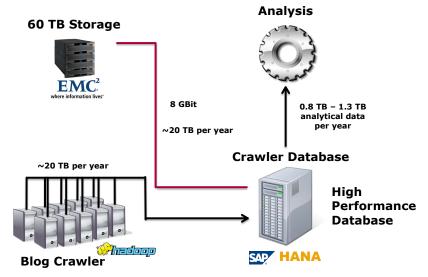

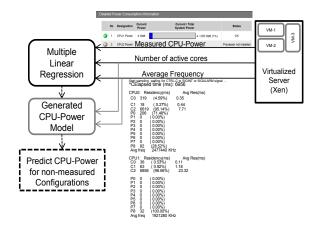

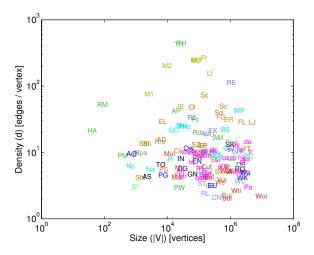

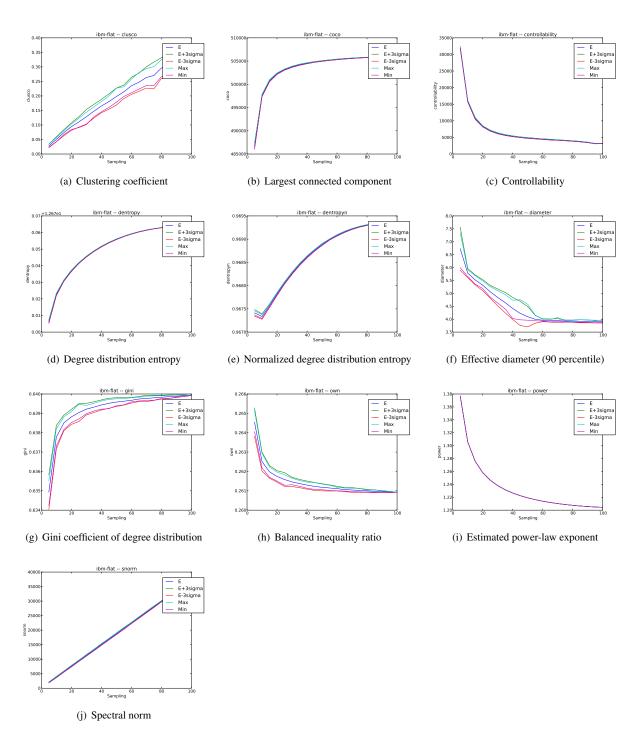

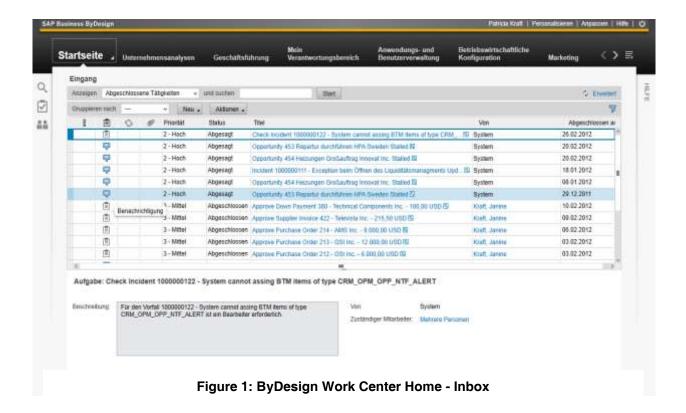

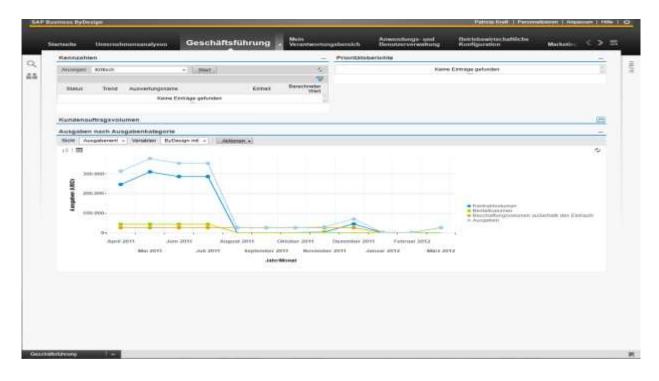

- [3] Roschke, S., Cheng, F., Meinel, Ch.: A New Correlation Algorithm based on Attack Graph. In: Proceedings of the 4th Conference on Computational Intelligence in Security for Information Systems (CISIS'11), Springer LNCS 6694, Torremolinos, Spain, pp. 58-67 (2011).